Product Summary

The PM8354A-N is an octal PHYsical layer transceiver ideal for systems requiring large numbers of point-to-point gigabit links. It provides eight individual serial channels capable of operation at up to 1.25 Gbps, which may be grouped together to form a single 12.5 Gbps bidirectional link. The applications of the PM8354A-N include High speed serial backplanes, Gigabit Ethernet links, FibreChannel links, Intra-system interconnect, ASIC to PMD link.

Features

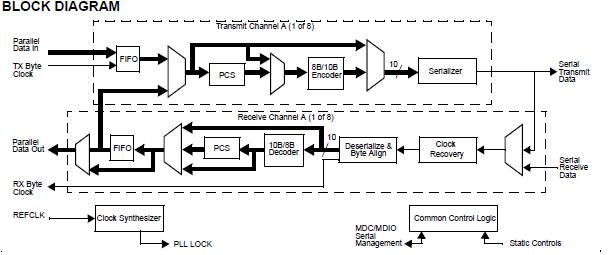

PM8354A-N features: (1)Eight independent 1.0-1.25 Gbit/s transceivers; (2)Ultra low power operation: 1.25 Watts typical; (3)Integrated serializer/deserializer, clock synthesis, clock recovery, and 8B/10B encode/decode logic; (4)Physical Coding Sublayer (PCS) logic for Gigabit Ethernet; (5)Optional receive FIFO which synchronizes incoming data to local; (6)clock domain; (7)Dual Data Rate (DDR) parallel interface with clock forwarding to halve ASIC terminal count and simplify timing; (8)Extensive control of loopback, BIST, and operating modes via 802.3 compliant MDC/MDIO serial interface; (9)Built-in packet generator/checker; (10)Trunking feature to de-skew and align received parallel data across eight channels; (11)IEEE 1149.1 JTAG testing support; (12)IEEE 802.3z Gigabit Ethernet and ANSI X3T11 FibreChannel support; (13)High speed outputs which feature programmable output current to; (14)directly drive dual-terminated line; (15)2.5 V, 0.25 ?CMOS technology with 3.3V tolerant I/O; (16)Direct interface to optical modules, coax, or serial backplanes; (17)Small footprint 19x19 mm, 289-pin PBGA.

Diagrams

(China (Mainland))

(China (Mainland))