Product Summary

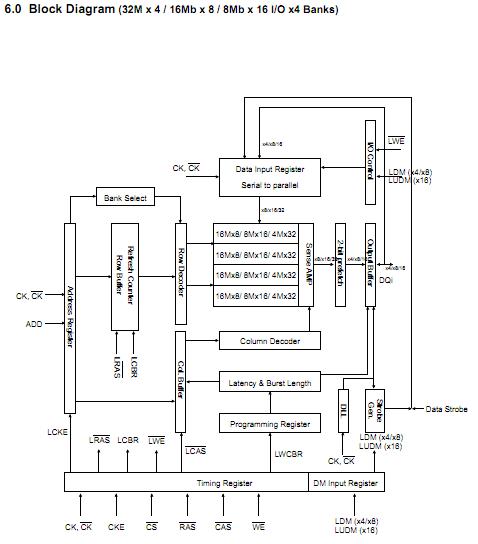

The K4H510838B-TCCC is a 536,870,912 bits, double data rate synchronous DRAM organized as 4× 33,554,432/ 4× 16,777,216 / 4× 8,388,608 words by 4/8/16bits, fabricated with SAMSUNG’s high performance CMOS technology. Synchronous features with Data Strobe allow extremely high performance up to 400Mb/s per pin. I/O transactions are possible on both edges of DQS. Range of operating frequencies, programmable burst length and programmable latencies allow the K4H510838F-LCCC to be useful for a variety of high performance memory system applications.

Parametrics

K4H510838B-TCCC absolute maximum ratings: (1)Voltage on any pin relative to VSS, VIN, VOUT: -0.5 ~ 3.6 V; (2)Voltage on VDD & VDDQ supply relative to VSS, VDD, VDDQ: -1.0 ~ 3.6 V; (3)Storage temperature, TSTG: -55 ~ +150℃; (4)Short circuit current, IOS: 50 mA.

Features

K4H510838B-TCCC features: (1)VDD: 2.5V ± 0.2V, VDDQ: 2.5V ± 0.2V for DDR266, 333; (2)VDD: 2.6V ± 0.1V, VDDQ: 2.6V ± 0.1V for DDR400; (3)Double-data-rate architecture; two data transfers per clock cycle; (4)Bidirectional data strobe [DQS] (×4,×8) & [L(U)DQS] (×16) ; (5)Four banks operation; (6)Differential clock inputs(CK and CK); (7)DLL aligns DQ and DQS transition with CK transition; (8)MRS cycle with address key programs; (9)All inputs except data & DM are sampled at the positive going edge of the system clock(CK); (10)Data I/O transactions on both edges of data strobe ; (11)Edge aligned data output, center aligned data input; (12)LDM,UDM for write masking only (×16); (13)DM for write masking only (×4, ×8); (14)Auto & Self refresh; (15)7.8us refresh interval(8K/64ms refresh) ; (16)Maximum burst refresh cycle: 8; (17)66pin TSOP II Lead-Free & Halogen-Free package.

Diagrams

(China (Mainland))

(China (Mainland))