Product Summary

The H5RS5223DFR-20C is a 512Mbit (16Mx32) GDDR3 SDRAM. The H5RS5223DFR-20C uses a double data rate architecture to achieve high-speed opreration. The double date rate architecture is essentially a 4n-prefetch architecture, with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the Hynix H5RS5223DFR-20C consists of a 4n-bit wide, every two-clock-cycles data transfer at the internal DRAM core and two corresponding n-bit wide, one-half-clock-cycle data transfers at the I/O pins. The address bits registered coincident with the READ or WRITE command are used to select the starting column location for the burst access. Prior to normal operation, the HynixH5RS5223DFR-20C must be initialized.

Parametrics

H5RS5223DFR-20C absolute maximum ratings: (1)Voltage on Vdd Supply Relative to Vss: -0.5 to +2.5 V; (2)Voltage on VddQ Supply Relative to Vss: -0.5 to 2.5 V; (3)Voltage on Vref and Inputs Relative to Vss: -0.5 to 2.5 V; (4)Storage Temperature: -55 to +150°C; (5)Short Circuit Output Current: 50mA.

Features

H5RS5223DFR-20C features: (1)2.05V/ 1.8V/ 1.5V power supply supports (For more detail, Please see the Table 12 on page 43); (2)Single ended READ Strobe (RDQS) per byte; (3)Single ended WRITE Strobe (WDQS) per byte; (4)Internal, pipelined double-data-rate (DDR) architecture; two data accesses per clock cycle; (5)On Die Termination; (6)Output Driver Strength adjustment by EMRS; (7)Calibrated output driver; (8)Differential clock inputs (CK and CK#); (9)Commands entered on each positive CK edge; (10)RDQS edge-aligned with data for READ; with WDQS center-aligned with data for WRITE; (11)8 internal banks for concurrent operation; (12)CAS Latency: 4~11 (clock); (13)Data mask (DM) for masking WRITE data; (14)4n prefetch; (15)Programmable burst lengths: 4, 8; (16)32ms, 8K-cycle auto refresh; (17)Auto precharge option; (18)Auto Refresh and Self Refresh Modes; (19)1.8V Pseudo Open Drain I/O; (20)Concurrent Auto Precharge support; (21)tRAS lockout support, Active Termination support; (22)Programmable Write latency(1, 2, 3, 4, 5, 6); (23)Boundary Scan Function with SEN pin; (24)Mirror Function with MF pin.

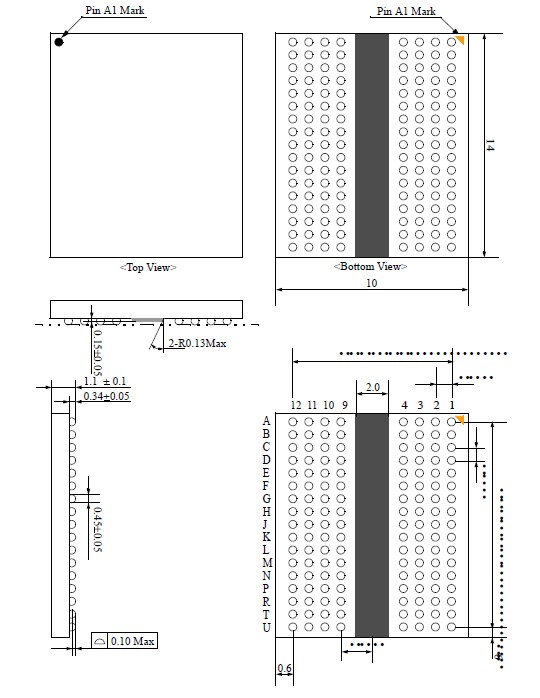

Diagrams

(China (Mainland))

(China (Mainland))