Product Summary

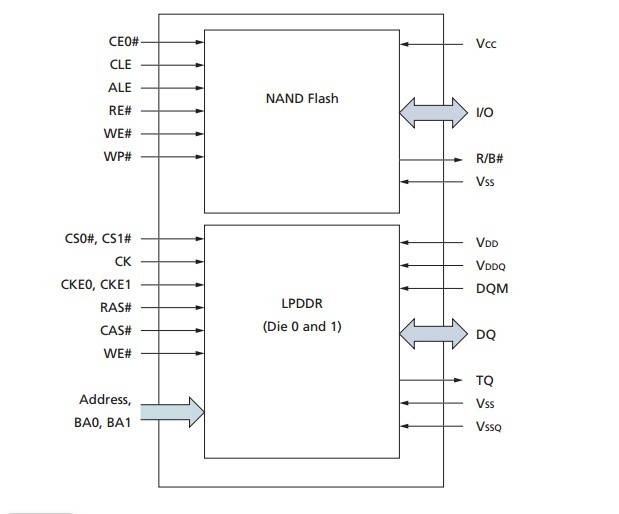

The MT29C2G24MAKJAJC-75IT is a micron package-on-package (PoP) MCP. The MT29C2G24MAKJAJC-75IT is packaged with separate interfaces (no shared address, control, data, or power balls). This bus architecture supports an optimized interface to processors with separate NAND Flash and Mobile LPDRAM buses. The NAND Flash and Mobile LPDRAM devices have separate core power connections and share a common ground (that is, VSS is tied together on the two devices). The bus architecture of this device also supports separate NAND Flash and Mobile LPDRAM functionality without concern for device interaction.

Parametrics

MT29C2G24MAKJAJC-75IT absolute maximum ratings: (1)Voltage input (1.8V): -0.6 to 2.4 V; (2)Voltage input (3.3V): -0.6 to 4.6 V; (3)Storage temperature range: -65 to 150 °C; (4)VCC supply voltage (1.8V): -0.6 to 2.4 V; (5)VCC supply voltage (3.3V): -0.6 to 4.6 V; (6)Short circuit output current, I/Os: 5 mA; (7)LINE REGULATION: +/-1.0%; (8)AC CURRENT: 1.85A / 115VAC or 1A / 230VAC; (9)INRUSH CURRENT (max.): 120A / 230VAC.

Features

MT29C2G24MAKJAJC-75IT features: (1)Micron-NAND Flash and LPDDR components; (2)RoHS-compliant, green package; (3)Separate NAND Flash and LPDDR interfaces; (4)Space-saving multichip package/package-on-package combination; (5)Low-voltage operation (1.70+/-0.95V); (6)No external voltage reference required; (7)No minimum clock rate requirement; (8)1.8V LVCMOS-compatible inputs; (9)Programmable burst lengths; (10)Partial-array self refresh (PASR); (11)Deep power-down (DPD) mode; (12)Selectable output drive strength; (13)STATUS REGISTER READ (SRR) supported.

Diagrams

(China (Mainland))

(China (Mainland))