Product Summary

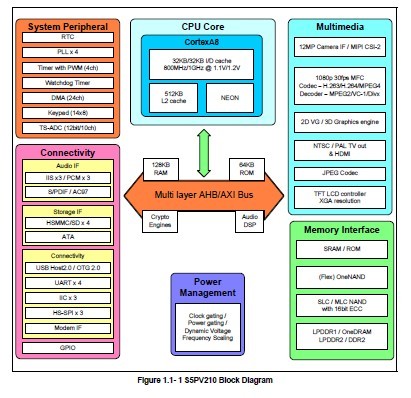

The S5PV210AA0-LA40 is a 32-bit RISC cost-effective, low power, high performance microprocessor solution for mobile phones and general applications, and integrates an ARM Cortex-A8 which implements the ARM architecture V7-A with supporting numerous peripherals. To provide optimized Hardware (H/W) performance for the 3G and 3.5G communication services, the S5PV210AA0-LA40 adopts 64-bit internal bus architecture and includes many powerful hardware accelerators for tasks such as motion video processing, display control and scaling.

Parametrics

S5PV210AA0-LA40 absolute maximum ratings: (1)Supply Voltage for Logic Core: VDD_INT 1.1V ±5%, VDD_ARM depends on operating frequency; (2)External Memory Interface: 1.2/1.8V; (3)External I/O Interface: 1.8/2.5/3.3V.

Features

S5PV210AA0-LA40 features: (1)ARM CortexTM-A8 based CPU Subsystem with NEON; (2)64-bit Multi-layer bus architecture; (3)MIPI-DSI and MIPI-CSI interface support; (4)1 AC-97 audio codec interface and 3-channel PCM serial audio interface; (5)3 24-bit I2S interface support; (6)1 TX only S/PDIF interface support for digital audio; (7)3 I2C interface support; (8)3 SPI support; (9)4 UART which support 3Mbps port for Bluetooth 2.0; (10)On-chip USB 2.0 OTG supporting high speed (480Mbps, on-chip transceiver); (11)On-chip USB 2.0 Host supporting; (12)Asynchronous Modem Interface support; (13)4 SD/SDIO/HS-MMC interface support.; (14)ATA/ATAPI-6 standard interface support.

Diagrams

(China (Mainland))

(China (Mainland))