Product Summary

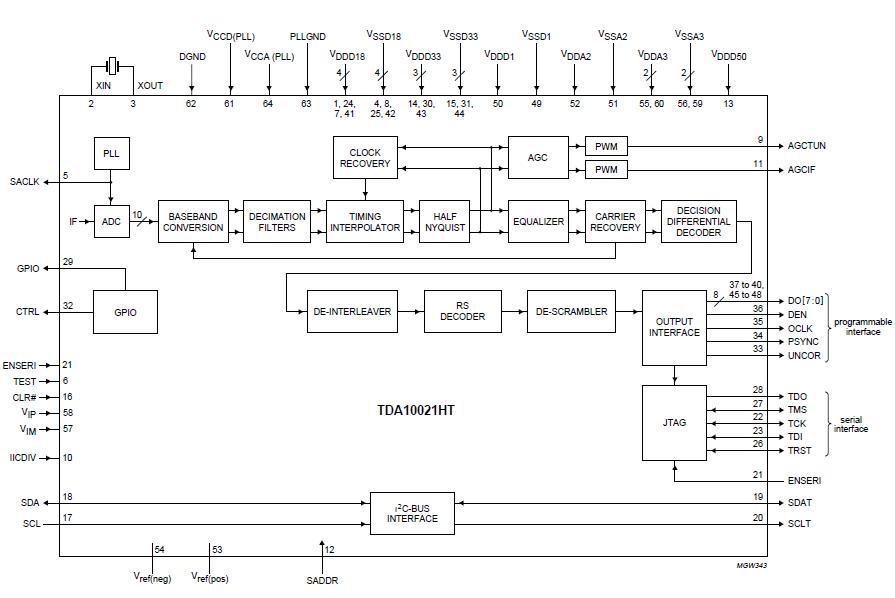

The TDA10023HT is a single-chip DVB-C channel receiver for 4, 16, 32, 64, 128 and 256 QAM modulated signals. The device interfaces directly to the IF signal, which is sampled by a 10-bit ADC. The TDA10023HT performs the clock and the carrier recovery functions. The digital loop filters for both clock and carrier recovery are programmable in order to optimize their characteristics according to the current application.

Parametrics

TDA10023HT absolute maximum ratings: (1)VDDD33, digital supply voltage for the pads: 2.97 to 3.63 V; (2)VDDD18, digital supply voltage for the core: 1.7 to 1.9 V; (3)VDDD50, digital supply voltage: 4.75 to 5.25 V; (4)VIH, HIGH-level input voltage: 2 to VDDD50 V; (5)VIL, LOW-level input voltage TTL input: 0 to 0.8 V; (6)VOH, HIGH-level output voltage: 2.4V; (7)VOL, LOW-level output voltage: 0.4 V; (8)IDDD33, digital supply current for the pads: 46 mA; (9)IDDD18, digital supply current for the corefs = 28.92 MHz; symbol rate = 7 Mbaud: 120mA; (10)Ptot, total power dissipation fs = 28.92 MHz; symbol rate = 7 Mbaud: 540 mW.

Features

TDA10023HT features: (1)4, 16, 32, 64, 128 and 256 Quadrature Amplitude Modulation (QAM) demodulator (DVB-C compatible: ETS 300-429/ITU-T J83 annex A/C); (2)High performance for 256 QAM, especially for direct IF applications; (3)On-chip 10-bit Analog-to-Digital Converter (ADC); (4)On-chip Phase-Locked Loop (PLL) for crystal frequency multiplication (typically 4 MHz crystal); (5)Digital downconversion; (6)Programmable half Nyquist filter (roll off = 0.15 or 0.13); (7)Two Pulse Width Modulated (PWM) AGC outputs with programmable take over point (for tuner and down converter control); (8)Clock timing recovery, with programmable 2nd-order loop filter; (9)Variable symbol rate capability from SACLK/64 to SACLK/4 (SACLK = 36 MHz maximum); (10)Programmable anti-aliasing filters; (11)Full digital carrier recovery loop; (12)Carrier acquisition range up to 18% of symbol rate.

Diagrams

(China (Mainland))

(China (Mainland))