Product Summary

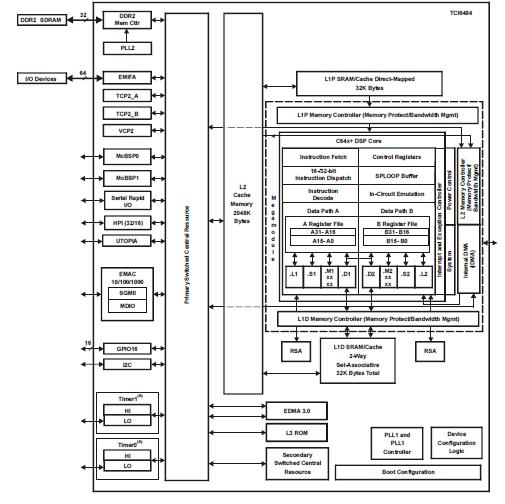

The TMS320TCI6484CMH is a digital signal processor. The TMS320TCI6484CMH device is based on the third-generation high-performance, advanced VelociTI. very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making the DSP an excellent choice for applications including video and telecom infrastructure, imaging/medical, and wireless infrastructure (WI). The TMS320TCI6484CMH device is upward code-compatible from previous devices that are part of the C6000. DSP platform.

Parametrics

TMS320TCI6484CMH absolute maximum ratings: (1)CVDD: -0.3 V to 1.35 V; (2)DVDD18: -0.3 V to 2.45 V; (3)DVDD33: -0.3 V to 3.60V; (4)VREFSSTL: 0.49 × DVDD18 to 0.51 × DVDD18; (5)VDD11, VDDD11, VDDT11: -0.3 V to 1.35 V; (6)VDDR18: -0.3 V to 2.45 V; (7)AVDD118, AVDD218: -0.3 V to 2.45 V; (8)VSS Ground: 0 V; (9)Commercial, 1-GHz CPU: 0℃ to 100℃; 1.2-GHz CPU: 0℃ to 95℃; (10)Extended, 1-GHz CPU: -40℃ to 100℃; 1.2-GHz CPU: -40℃ to 95℃; (11)Storage temperature range, Tstg: -65℃ to 150℃.

Features

TMS320TCI6484CMH features: (1)High-Performance Fixed-Point DSP (TCI6484), 1-ns and 0.83-ns; Instruction Cycle Time; 1-GHz and 1.2 GHz Clock Rate; Eight 32-Bit Instructions/Cycle; 8000 and 9600 MIPS/MMACS (16-Bits); Case Temperature, Commercial: 0 to 100℃(1 GHz); 0 to 95℃(1.2 GHz); Extended: -40 to 100℃ (1 GHz); -40 to 95℃ (1.2 GHz); (2)TMS320C64x+ DSP Core, Dedicated SPLOOP Instruction; Compact Instructions (16-Bit); Instruction Set Enhancements; Exception Handling; (3)TMS320C64x+ Megamodule L1/L2 Memory Architecture: 256K-Bit (32K-Byte) L1P Program Cache [Direct Mapped]; 256K-Bit (32K-Byte) L1D Data Cache [2-Way Set-Associative]; 16M-Bit (2048K-Byte) L2 Unified Mapped Ram/Cache [Flexible Allocation]; Configurable up to 1MB of L2 Cache; 512K-Bit (64K-Byte) L3 ROM; Time Stamp Counter.

Diagrams

(China (Mainland))

(China (Mainland))