Product Summary

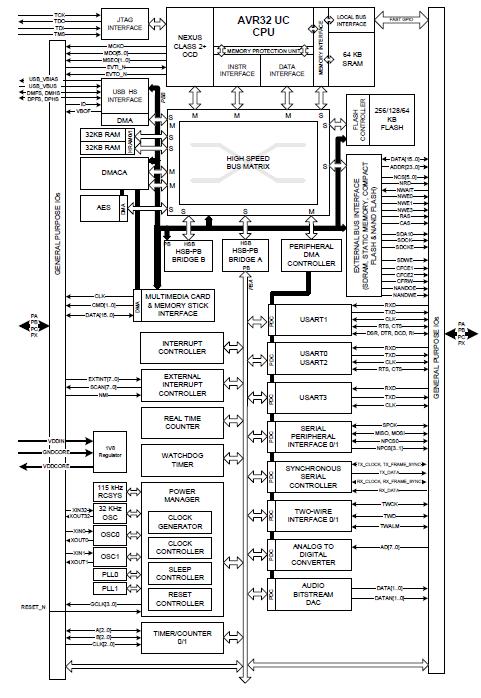

The 32UC3A3256-U is a complete System-On-Chip microcontroller based on the AVR32 UC RISC processor running at frequencies up to 66MHz. AVR32 UC is a high-performance 32-bit RISC microprocessor core, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption, high code density and high performance. The 32UC3A3256-U implements a Memory Protection Unit (MPU) and a fast and flexible interrupt controller for supporting modern operating systems and real-time operating systems. Higher computation capabilities are achievable using a rich set of DSP instructions.

Parametrics

32UC3A3256-U absolute maximum ratings: (1)Operating Temperature: -40℃ to +85℃; (2)Storage Temperature: -60℃ to +150℃; (3)Voltage on Input Pin with respect to Ground: -0.3V to 3.6V; (4)Maximum Operating Voltage (VDDCORE): 1.95V; (5)Maximum Operating Voltage (VDDIO): 3.6V; (6)Total DC Output Current on all I/O Pin for TQFP144 package: 370 mA; for TFBGA144 package: 370 mA.

Features

32UC3A3256-U features: (1)High Performance, Low Power 32-bit AVR?Microcontroller, Compact Single-Cycle RISC Instruction Set Including DSP Instruction Set; Read-Modify-Write Instructions and Atomic Bit Manipulation; Performing up to 1.51DMIPS/MHz, Up to 92DMIPS Running at 66MHz from Flash (1 Wait-State); Up to 54 DMIPS Running at 36MHz from Flash (0 Wait-State); (2)Memory Protection Unit, Multi-Layer Bus System; High-Performance Data Transfers on Separate Buses for Increased Performance; 8 Peripheral DMA Channels (PDCA) Improves Speed for Peripheral; (3)Communication; 4 generic DMA Channels for High Bandwidth Data Paths; (4)Internal High-Speed Flash, 256KBytes, 128KBytes, 64KBytes versions; Single-Cycle Flash Access up to 36MHz; Prefetch Buffer Optimizing Instruction Execution at Maximum Speed; 4 ms Page Programming Time and 8ms Full-Chip Erase Time; (5); 100,000 Write Cycles, 15-year Data Retention Capability; Flash Security Locks and User Defined Configuration Area; (6)Internal High-Speed SRAM, 64KBytes Single-Cycle Access at Full Speed, Connected to CPU Local Bus; 64KBytes (2x32KBytes with independent access) on the Multi-Layer Bus System; (7)Interrupt Controller, Autovectored Low Latency Interrupt Service with Programmable Priority; (8)System Functions; Power and Clock Manager Including Internal RC Clock and One 32KHz Oscillator; Two Multipurpose Oscillators and Two Phase-Lock-Loop (PLL), Watchdog Timer, Real-Time Clock Timer.

Diagrams

(China (Mainland))

(China (Mainland))