Product Summary

The H5MS5162DFR-E3M-C is 536,870,912-bit CMOS Low Power Double Data Rate Synchronous DARM ( Mobile DDR SDRAM) , ideally suited for mobile applications which use the battery such as PDAs, 2.5G and 3G cellular phones. The H5MS5162DFR-E3M-C uses a double-data-rate architecture to achieve high-speed operation. The H5MS5162DFR-E3M-C offers fully synchronous operations referenced to both rising and falling edges of the dock.

Parametrics

H5MS5162DFR-E3M-C absolute maximum ratings: (1) Operating Case Temperature TC: -30°C to 85°C; (2) Storage Temperature TSTG: -55°C to 150°C; (3) Voltage on Any Pin relative to VSS, VIN, VOUT: -0.3V, VDDQ +0.3V; (4) Voltag on VDD relative to VSS, VDD: -0.3V to 2.7V; (5) Voltage on VDDQ relative to VSS, VDDQ: -0.3V to 2.7V; (6) Short Circuit Output Current IOS: 50mA; (7) Power Dissipation, PD: 0.7W.

Features

H5MS5162DFR-E3M-C features: (1) Mobile DDR SDRAM; (2) Mobile DDR SDRAM Interface; (3) Supply Voltage; (4) Memory Cell Array; (5) Data Storbe; (6) Cas Latency; (7) Burst Length; (8) Clock Stop Mode.

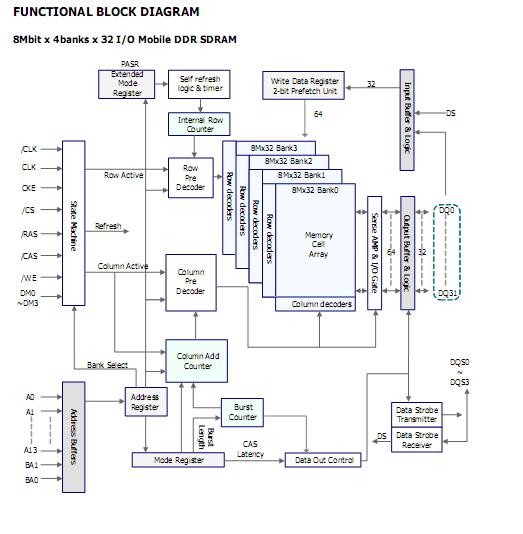

Diagrams

(China (Mainland))

(China (Mainland))